对

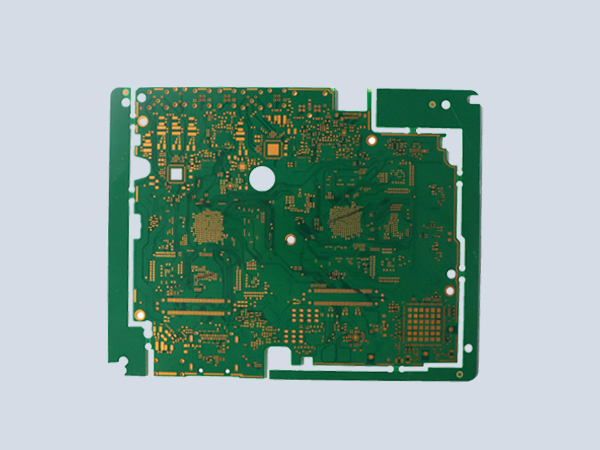

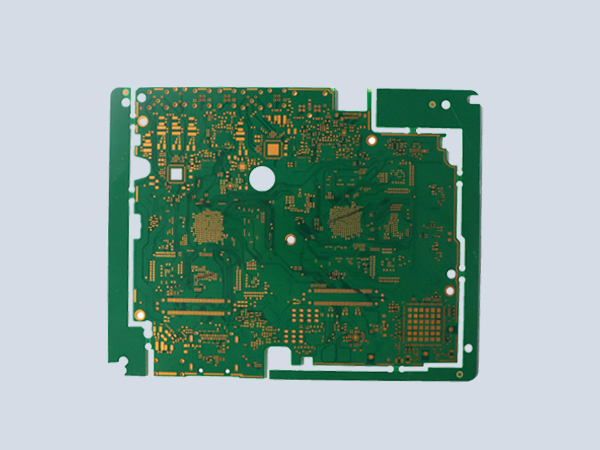

PCB线路板电子行业来说,据行内调查,化学镀锡层最致命的弱点就是易变色(既易氧化或潮解)、钎焊性差导致难焊接、阻抗过高导致导电性能差或整板性能的不稳定、易长锡须导致PCB线路短路以至烧毁或着火事件。

据悉,国内最先研究化学镀锡的当是上世纪90年代初昆明理工大学,之后就是90年代末的广州同谦化工(企业),一直至今,10年来行内均有认可该两家机构是做得最好的。其中,据我们对众多企业的接触筛选调查、实验观测以及长期耐力测试,证实同谦化工的镀锡层是低电阻率的纯锡层,导电和钎焊等质量可以保证到较高的水准,难怪他们敢对外保证其镀层在无须任何封闭及防变色剂保护的情况下,能保持一年不变色、不起泡、不脱皮、永久不长锡须。

后来当整个社会生产业发展到一定程度的时候,很多后来参与者往往是属于互相抄袭,其实相当一部分企业自己本身并没有研发或首创能力,所以,造成很多产品及其用户的电子产品(电路板板底或电子产品整体)性能不佳,而造成性能不佳的最主要原因就是因为PCB电路板阻抗问题,因为当不合格的化学镀锡技术在使用过程中,其为PCB线路板所镀上去的锡其实并不是真正的纯锡(或称纯金属单质),而是锡的化合物(即根本就不是金属单质,而是金属化合物,氧化物或卤化物,更直接地说是属于非金属物质)或锡化合物与锡金属单质的混合物,但单凭借肉眼是很难发现的。

因为PCB线路板的主体线路是铜箔,在铜箔的焊点上就是镀锡层,而电子元件就是通过焊锡膏(或焊锡线)焊接在镀锡层上面的,事实上焊锡膏在融熔状态焊接到电子元件和锡镀层之间的是金属锡(即导电良好的金属单质),所以可以简单扼要地指出,电子元件是通过锡镀层再与PCB板底的铜箔连接的,所以锡镀层的纯洁性及其阻抗是关键;又,但未有接插电子元件之前,我们直接用仪器去检测阻抗时,其实仪器探头(或称为表笔)两端也是通过先接触PCB板底的铜箔表面的锡镀层再与PCB板底的铜箔来连通电流的。所以锡镀层是关键,是影响阻抗的关键和影响PCB整板性能的关键,也是易于被忽略的关键。

众所周知,除金属单质外,其化合物均是电的不良导体或甚至不导电的(又,这也是造成线路中存在分布容量或传布容量的关键),所以锡镀层中存在这种似导电而非导电的锡的化合物或混合物时,其现成电阻率或未来氧化、受潮所发生电解反应后的电阻率及其相应的阻抗是相当高的(足已影响数字电路中的电平或信号传输,)而且其特征阻抗也不相一致。所以会影响该线路板及其整机的性能。

所以,就现时的社会生产现象来说,PCB板底上的镀层物质和性能是影响PCB整板特征阻抗的最主要原因和最直接的原因,但又由于其具有随着镀层老化及受潮电解的变化性,所以其阻抗产生的忧患影响变得更加隐性和多变性,其隐蔽的主要原因在于:第一不能被肉眼所见(包括其变化),第二不能被恒常测得,因为其有随着时间和环境湿度的改变而变的变化性,所以总是易于被人忽略。

pcb线路板阻抗及其影响因素 阻抗控制(eImpedace Controling),线路板中的导体中会有各种信号的传递,为提高其传输速率而必须提高频率,线路本身若因蚀刻,叠层厚度,导线宽度等不同因素,将会造成阻抗值的变化,使得信号失真。故在高速线路板上的导体,其阻抗值应该控制在某一范围内,称谓“阻抗控制”。

在实际情况中,一般数字信号边沿低于 1ns 或者模拟频率超过 300MHz 时就需要控制阻抗了。印制电路板上导线的特性阻抗是电路板设计的一个重要指标,特别是在高频电路的 PCB 设计中,必须考虑导线的特性阻抗和器件或信号所要求的特性阻抗是否一致,是否匹配。

PCB迹线的阻抗将由其感应和电容性电感、电阻和电导系数确定。影响 PCB 走线的阻抗的因素主要有: 铜线的宽度、铜线的厚度、介质的介电常数、介质的厚度、焊盘的厚度、地线的路径、走线周边的走线等。PCB 阻抗的范围是 25 至 120 欧姆[1]。注:本文大部分参考自[1],在此对原作者表示感谢。

在实际情况下,PCB 传输线路通常由一个导线迹线、一个或多个参考层和绝缘材质组成。迹线和板层构成了控制阻抗。PCB 将常常采用多层结构,并且控制阻抗也可以采用各种方式来构建。但是,无论使用什么方式,阻抗值都将由其物理结构和绝缘材料的电子特性决定:

信号迹线的宽度和厚度

迹线两侧的内核或预填材质的高度

迹线和板层的配置

内核和预填材质的绝缘常数

这里需要注意了解的是,阻抗控制/匹配主要是指信号层与相邻的参考平面层之间。